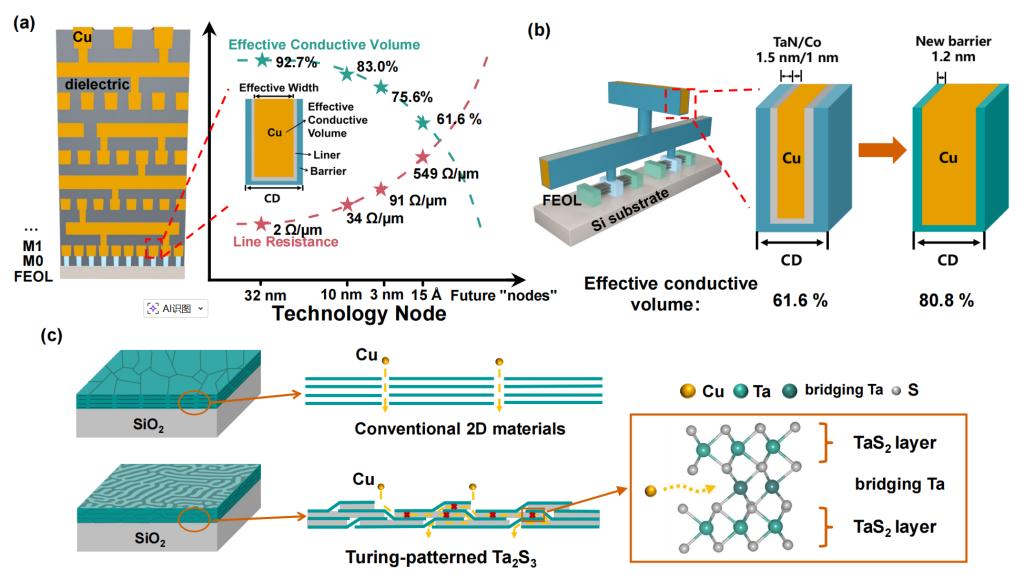

随着集成电路持续向15 Å节点及以下演进,后道金属互连的RC延迟加剧已成为制约芯片性能提升的重要瓶颈。传统TaN/Ta或TaN/Co等双层结构虽然能够提供必要的扩散阻挡与界面可靠性,但其厚度难以随互连尺寸同步缩减,导致Cu有效导电体积不断被压缩,严重限制先进互连进一步缩放。与此同时,现有二维层状阻挡材料仍普遍面临制备温度高、层间易扩散及界面黏附不足等问题。因此,开发兼具超薄化、界面可靠性与阻挡性能的先进扩散阻挡层,已成为先进互连领域的重要研究方向。

为应对上述挑战,电子游艺

深圳研究生院电子游艺

王新炜团队提出了一种图灵图案化Ta2S3(Tp-Ta2S3)超薄阻挡层设计策略。通过构筑具有迷宫状条纹形貌和交织层状结构的功能薄膜,实现了对Cu扩散路径、层间迁移能垒及界面黏附行为的协同调控,为先进节点铜互连阻挡层的材料设计提供新的研究路径。

团队发展了基于TBTDET前驱体与H2S等离子体的能量增强原子层沉积方法,在后道兼容温度下成功制备出厚度仅约1.2 nm的Tp-Ta2S3薄膜。研究表明,该材料中的桥接Ta原子能够显著提高Cu层间扩散能垒,并增强层间结合力,从而有效克服传统二维层状材料中层间扩散快、界面黏附弱的问题。

性能测试表明,Tp-Ta2S3具有优异的Cu润湿性和界面稳定性,其界面黏附能达到10.33 J/m2;在TDDB测试中,仅1.2 nm厚的Tp-Ta2S3即表现出优于2.5 nm TaN的扩散阻挡性能,展现出显著的超薄化应用优势。进一步研究还表明,该材料可在高深宽比沟槽侧壁实现保形沉积,并可在Co/SiO2图形结构上实现选择性沉积,显示出良好的先进互连集成潜力。

图1. 图灵图案化Ta2S3超薄扩散阻挡层的结构设计与先进Cu互连应用示意图

综上,本研究提出并验证了一种面向先进互连缩放瓶颈的图灵图案化超薄阻挡层新策略。通过构筑具有交织层状特征和桥接层间结构的Tp-Ta2S3薄膜,研究团队成功克服了传统二维层状阻挡材料在层间扩散和界面黏附方面的本征局限,实现了亚2 nm尺度下扩散阻挡性能、界面稳定性和工艺集成性的协同提升。该工作不仅为高性能、低RC延迟先进Cu互连材料设计提供了新思路,也为后摩尔时代先进集成电路互连技术的发展奠定了重要科学基础。

相关研究成果以 “Turing-patterned Ta2S3 enables sub-2 nm diffusion barrier for advanced Cu interconnects” 为题,发表于国际综合性学术期刊《Nature Communications》。

电子游艺

深圳研究生院电子游艺

王新炜长聘副教授为该论文通讯作者,我院博士生田旭为论文第一作者。该研究工作得到了国家自然科学基金、深圳市基础研究项目、北京市杰出青年科学基金、111计划等资助,并依托电子游艺

高性能计算平台、电子游艺

核物理与核技术国家重点实验室开放课题以及广东省氧化物半导体器件与集成电路技术中心等平台支持。

论文链接: //doi.org/10.1038/s41467-026-71545-2